在分析乘法的步驟中我們可以觀察到若是加法左移和右移各需要一個時鐘周期

那32位元的乘法器就需要近一百個時鐘周期來完成

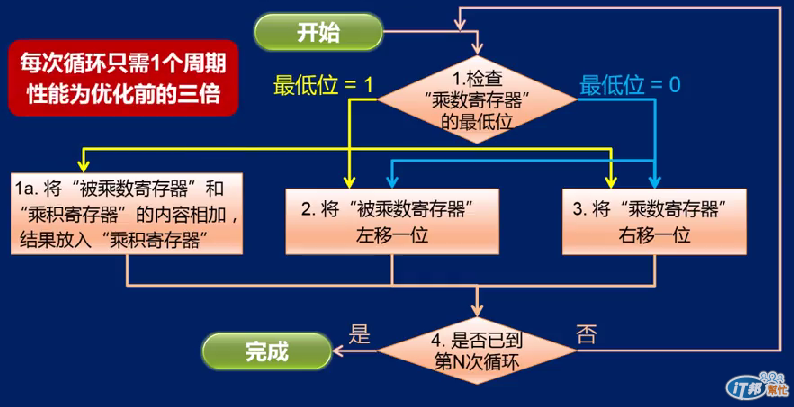

因此在進行乘法器的優化時,首先就可以考慮是否能將這三個運算在同個時鐘周期平行處理

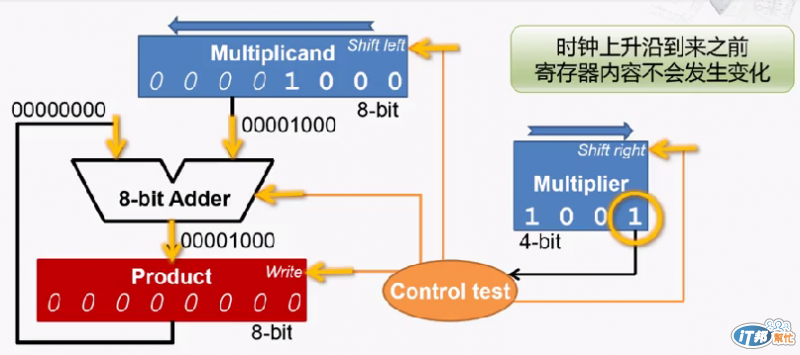

在暫存器的實現中我們有提到,在時鐘上升延到來之前暫存器內容是不會產生任何變化的

因此在上升延到來期間,控制信號可以藉由觀察乘數的最低位元來控制是否進行加法

而且也可以同時設置左移及右移訊號,這樣在時鐘上升延到來之後,三個暫存器就可以同時進行寫入的工作

經過修改流程圖之後每次循環都只要一個周期,性能也就優化為最原始的三倍了~!!

當然乘法器也可以透過同時平行處理中間檔案,最後再將結果加起來

這部分老師就沒有多加著墨,有興趣的人只好自己多找資料囉~!!